Based on the advanced NXP ARM and SoC chip platform, CKTECH independently developed 5G RAN protocol stack including L1 physical layer and L2/L3 high-level protocol stack software. CKTECH can provide customization services for 5G NR protocol stack software and main boards to help 5G product development and empower 5G RAN ecosystem.

1. L1 Physical Layer protocol stack

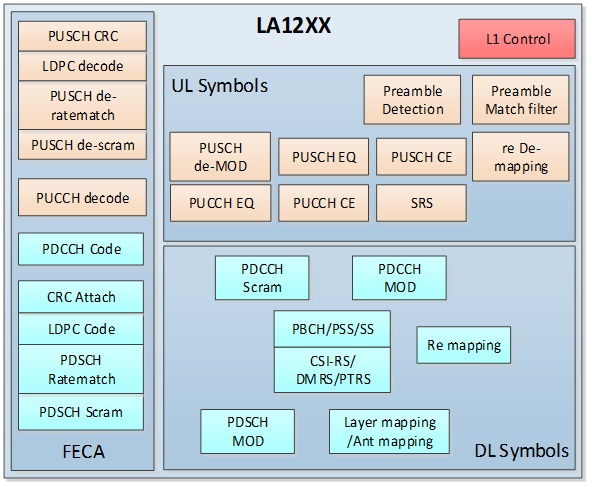

Based on the NXP LA12XX SoC chip, CKTECH has completed the software R&D of the 5G NR physical layer protocol stack with fully independent intellectual property rights. Based on NXP LA12XX SoC chip more than 90% of the physical layer protocol stack software have been implemented and optimized in assembly language to improve the overall operational efficiency and optimize the performance of 5G RAN physical layer. CKTECH can provide the customized R&D of 5G RAN physical layer protocol stack according to customer’s requirement.

The 5G NR physical layer protocol stack software architecture is shown in the figure below.

L1 physical layer protocol stack software architecture

L1 Physical Layer protocol stack functions and features are shown as below:

a) Based on NXP SoC chip, the complete High-PHY and Low-PHY functions of 5G RAN physical layer are implemented.

b) 5G RAN physical layer core algorithm has been researched and optimized independently for physical layer code simulation and logarithm to build a complete 5G RAN physical layer algorithm platform.

c) The physical layer parameter calculation function of e200 module on NXP SoC chip has completed all of 5G RAN physical layer processing and all parameters calculation of FECA bit-level accelerator.

d) The VSPA multi-core vector processor on NXP SoC chip has completely realized multi-user downlink symbol level processing and the functions of uplink multi-user signal channel estimation, balancing, MMSE receiver etc.

e) In order to improve the processing efficiency, more than 90% of the 5G RAN physical layer protocol stack software is implemented and optimized in assembly language on the basis of NXP LA12XX SoC chip.

2. L2/L3 High Level protocol stack

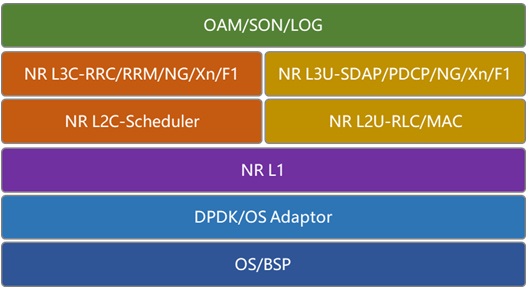

The software of 5G RAN L2/L3 high-level protocol stack based on NXP LX2160 16-core ARM chip is developed with fully independent intellectual property rights. The LX2160 has a built-in PDCP encryption and decryption hardcore that enables acceleration of encryption and decryption at the PDCP layer. The LX2160 supports multiple high-speed interfaces, including 10GE, 25GE, PCIe 4/8X, etc. The LX2160 also has a built-in high-performance transmission and routing accelerator to accelerate the transmission of user data. The high-level protocol stacks software based on LX2160 can be customized according to the customer’s requirement.

The high-level protocol stack software includes the OS layer, DPDK/OSA adaptation layer, NR L1 adaptation layer, NR L2 layer control plane (L2C) and L2 user plane (L2U), NR L3 layer control plane (L3C) and L3 user plane (L3U), and OAM/SON/LOG layer. 5G NR high level protocol stack software architecture is shown in the figure below.

L2/L3 high-level protocol stack software architecture

L2/L3 high-level protocol stack functions and features are shown as below:

a) Adopting our self-developed and optimized RT Linux operating system the impact on the real-time operation of the protocol stack has been eliminated.

b) DPDK enables a single ARM chip to perform user-plane data forwarding for multiple 4-antenna cells, and the OSA adaptation layer provides OS service encapsulation to better support resource allocation for upper-level software modules, such as memory resource allocation.

c) High-performance multi-cell multi-user scheduling is supported by operator-grade base station scheduler architecture, algorithms and algorithm implementation. It includes BWP switching, RB resource allocation, inner and outer ring AMC adjustment, uplink power control, service based QoS scheduling, VoNR supporting, schedule based on slicing, etc.

d) Multiple 4-antenna cells data throughput with a minimum number of cores is achieved by a large number of software optimizations on user-plane for the ARM architecture, and by the optimized DPDK together.

e) Adopting operator-grade base station control plane software architecture, RRM algorithm and the algorithm implementation, the high-level protocol stack software has improved cell and UE state management. It supports features such as broadcast management, RRC connection management, PDU Session management, Xn/Ng interface management, intra and inter-system mobility, VoNR and industry slicing, etc.

f) The protocol stack software supports improved OAM function of base station and operator-grade database model. The OAM supports the external interface of network management based on TR069 and built-in WebUI for base station management operations.

g) The high-level protocol stack software supports SON functions including base station self-test, transmission self-establishment, Xn/Ng port self-healing, and base station power saving, to meet different customer’s requirement.

h) The self-developed supporting debugging tools have provided internal Log and signaling tools, greatly improved the efficiency of analyzing and locating problems. The debugging tools has a user-friendly interface, which is powerful and can be continuously evolved.

+86-10-62060415